Mips32 addi

Autor/Urheber:

Attribution:

Das Bild ist mit 'Attribution Required' markiert, aber es wurden keine Informationen über die Attribution bereitgestellt. Vermutlich wurde bei Verwendung des MediaWiki-Templates für die CC-BY Lizenzen der Parameter für die Attribution weggelassen. Autoren und Urheber finden für die korrekte Verwendung der Templates hier ein Beispiel.

Shortlink:

Quelle:

Größe:

500 x 180 Pixel (15706 Bytes)

Beschreibung:

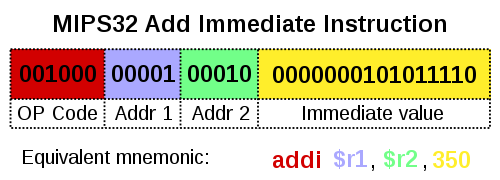

This figure demonstrates how one type of MIPS32 instruction word is decoded. The first six bits specify the operation (add immediate). The second and third groups of five bits each specify the number of one of MIPS32's 32 general-purpose registers (GPR). The first group specifies the destination GPR, and the second specifies the source GPR. The last sixteen bits specify the immediate value, that is, the 16-bit signed (two's compliment) integer that is added to the second register and then stored in the first register. The equivalent mnemonic in MIPS32 assembly is also shown. This instruction word would cause a MIPS32 CPU to add 350 to the value stored in $r2 and store the result in $r1. If an arithmetic overflow occurs, $r1 is not modified and an overflow flag is set.

Kommentar zur Lizenz:

Du darfst es unter einer der obigen Lizenzen deiner Wahl verwenden.

Lizenz:

Relevante Artikel

BefehlssatzDer Befehlssatz, auch Instruktionssatz, eines Prozessors ist in der Rechnerarchitektur die Menge der Maschinenbefehle, die ein bestimmter Prozessor ausführen kann. Je nach Prozessor variiert der Umfang des Befehlssatzes zwischen beispielsweise 33 und über 500 Befehlen. CISC-Prozessoren haben tendenziell größere Befehlssätze als RISC-Prozessoren, gleiches gilt für neuere Prozessoren gegenüber älteren Prozessoren. .. weiterlesen