Translation Lookaside Buffer

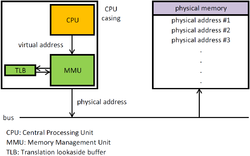

Der Begriff Übersetzungspuffer oder englisch Translation Lookaside Buffer (TLB, vgl. auch Cache) bezeichnet eine funktionale Einheit der Speicherverwaltung von selbst nachladenden Speicherverwaltungseinheiten (MMU).

Wenn virtueller Speicher verwendet wird, muss zu den virtuellen Adressen die jeweils zugehörige physische Adresse ermittelt werden. Dabei wird die virtuelle oder logische Adresse beim x86 in meist drei Arbeitsschritten mit Hilfe der Segment- und der meist baumartig organisierten Seitentabelle zur physischen Adresse umgesetzt, andere Prozessoren (ARM, PowerPC, MIPS etc.) arbeiten ähnlich. Da diese Arbeitsschritte verhältnismäßig zeitintensiv sind, werden die zuletzt ermittelten Werte für die Adresse der physischen Speicherseite im TLB zwischengespeichert, wodurch erneute Zugriffe auf Adressen in dieser Seite nicht aufwändig neu ermittelt werden müssen, sondern aus dieser Liste entnommen werden können. Der TLB kann eine begrenzte Menge dieser Referenzen halten (üblicherweise nicht mehr als 1024 Einträge) und kann dadurch die Ausführung von Speicherzugriffen deutlich beschleunigen. Dies wird über assoziative Ordnungsregister realisiert, die parallele Zugriffe erlauben. Durch seinen Aufbau ist der TLB pro Eintrag vergleichsweise teuer gegenüber anderen flüchtigen Speichern wie z. B. RAM.

Page Global

Seit dem Intel Pentium Pro ist mit Page Global Enable (PGE) auf der x86-Architektur ein Flag implementiert, das es erlaubt, eine Speicherseite (englisch page) mit gesetztem G-Bit (für „global“) nach erfolgter Speicherumsetzung permanent im TLB vorzuhalten. Dadurch wird die Adresse, z. B. bei einem Prozesswechsel, nicht aus dem TLB entfernt. „PGE“ muss im Steuerregister CR4 eines x86-Prozessors aktiviert werden.[2]

Einzelnachweise

- ↑ Andrew S. Tanenbaum: Moderne Betriebssysteme. 2., überarbeitete Auflage. Pearson Studium, 2003, ISBN 3-8273-7019-1.

- ↑ Wolfram Schiffmann, Helmut Bähring, Udo Hönig: Technische Informatik 3 – Grundlagen der PC-Technologie. Springer-Verlag, Berlin, Heidelberg 2011, ISBN 978-3-642-16811-6, 2.3 Seitenorientierte Speicherverwaltung, S. 93 (eingeschränkte Vorschau in der Google-Buchsuche): „PGE (Page Global Enable): Nur wenn dieses Bit gesetzt ist, kann eine Seite durch ihr G-Bit (Global, s. u.) für so wichtig erklärt werden, dass ihre einmalig ausgeführte Adressumsetzung permanent im TLB gespeichert wird, also z. B. bei einem Prozesswechsel nicht daraus entfernt wird.“

Auf dieser Seite verwendete Medien

Autor/Urheber: Mdjango, Andrew S. Tanenbaum, Lizenz: CC BY-SA 3.0

Funktionsweise einer MMU