Harvard-Architektur

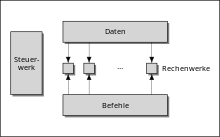

Die Harvard-Architektur bezeichnet in der Informatik ein Schaltungskonzept, bei dem der Befehlsspeicher logisch und physisch vom Datenspeicher getrennt ist. Die logische Trennung ergibt sich aus verschiedenen Adressräumen und verschiedenen Maschinenbefehlen zum Zugriff auf Befehl- und Datenspeicher. Die physische Trennung ist mit zwei getrennten Speichern realisiert, auf die der Zugriff über je einen eigenen Bus erfolgt. Bei einer weniger strikten Trennung von Befehls- und Datenspeichern spricht man von einer modifizierten Harvard-Architektur.

Motivation

Der Vorteil dieser Architektur besteht darin, dass Befehle und Daten gleichzeitig geladen bzw. geschrieben werden können. Bei einer klassischen Von-Neumann-Architektur sind hierzu mindestens zwei aufeinander folgende Buszyklen notwendig.

Zudem sorgt die physische Trennung von Daten und Programm dafür, dass Zugriffsrechtetrennung und Speicherschutz einfach realisierbar sind. Um z. B. zu verhindern, dass bei Softwarefehlern Programmcode überschrieben wird, kann Programmcode auf einem im Betrieb nur lesbaren Speicher (z. B. ROM, Lochkarten) liegen, Daten auf auch schreibbarem Speicher (z. B. RAM, Ringkernspeicher).

Geschichte

Der Name „Harvard-Architektur“ hat seinen Ursprung im elektromechanischen Computer Mark I, der in Kooperation zwischen IBM und der Harvard-Universität entwickelt und 1944 in Betrieb genommen wurde.

Die getrennten Speicher für Programme und Daten ergaben sich daraus, dass Befehle auf papiernen Lochstreifen und Daten auf Magnettrommeln gespeichert waren. 1945 postulierte John von Neumann, dass auch die Programme im Speicher des Computers stehen sollten. Diese Idee der Von-Neumann-Architektur setzte sich nach und nach durch.

Die Harvard-Architektur wurde zunächst überwiegend für RISC-Prozessoren wiedereingeführt. Moderne Prozessoren in Harvard-Architektur sind in der Lage, parallel mehrere Rechenwerke gleichzeitig mit Daten und Befehlen zu füllen. Bei Signalprozessoren der C6x-Familie von Texas Instruments ist dies beispielsweise für bis zu acht Rechenwerke möglich.

Ein weiterer Vorteil der Trennung ist, dass die Datenwortbreite (die kleinste adressierbare Einheit) und die Befehlswortbreite unabhängig voneinander festgelegt werden können. Damit kann auch, wenn erforderlich, die Effizienz des Programmspeicherbedarfs verbessert werden, da sie nicht direkt von den Datenbusbreiten abhängig ist, sondern ausschließlich vom Befehlssatz. Dies kann zum Beispiel in eingebetteten Systemen oder kleinen Mikrocontroller-Systemen von Interesse sein.

Single-Chip-Mikrocontroller, die mit festen Programmen arbeiten, haben meist Harvard-Architektur. Bekannte Vertreter sind zum Beispiel (PICmicro) von Microchip Technology, die Intel-Familien 8048 und 8051, der STM8 von STMicroelectronics und die AVR-Reihe von Microchip Technology.

Anfang der 1990er führte der amerikanische Hersteller Analog Devices die Erweiterung Super-Harvard-Architektur ein. Diese legt die genannten Speichersegmente in Dual-Port-RAMs aus, die kreuzweise zwischen den Programm- und Daten-Bussen liegen.

Viele moderne Prozessoren verwenden eine Mischform aus Harvard- und Von-Neumann-Architektur. Dabei werden innerhalb des Prozessorchips Daten und Programm getrennt verwaltet, haben eigene Caches und MMUs und laufen über getrennte interne Busse, extern liegen sie jedoch in einem gemeinsamen Speicher. Für eine Pipeline-Architektur hat es den Vorteil, dass deren einzelne Pipelinestufen in Bezug auf Speicherzugriffe getrennt werden können. Ein typisches Beispiel für diese Art Prozessoren ist der Motorola 68030, der in den 1980er Jahren entwickelt wurde.

Funktion

Die Funktion der Harvard-Architektur besteht darin, einen getrennten Zugriff auf Befehls- und Datenspeicher zu ermöglichen. Das bedeutet, dass die Befehle, die der Rechner ausführen soll, und die Daten, die er verarbeiten soll, in verschiedenen Speicherbereichen gespeichert werden. Diese Speicherbereiche haben jeweils einen eigenen Bus, also eine Verbindung zum Rechenwerk. Dadurch kann der Rechner gleichzeitig Befehle lesen und Daten schreiben oder umgekehrt, ohne dass es zu Konflikten oder Wartezeiten kommt. Außerdem kann der Rechner die Wortbreite der Befehle und der Daten unabhängig voneinander anpassen, je nachdem, wie viel Speicherplatz oder Rechenleistung er benötigt.[1]

Anwendung

Die Anwendung der Harvard-Architektur findet man vor allem in Bereichen, die eine hohe Leistungsfähigkeit und Effizienz des Rechners erfordern. Zum Beispiel wird die Harvard-Architektur oft in digitalen Signalprozessoren verwendet, die kontinuierlich große Mengen an Daten verarbeiten müssen, wie z. B. Audio- oder Videosignale. Die Harvard-Architektur ermöglicht es, die Signalverarbeitung in Echtzeit durchzuführen, indem sie die parallele Ausführung von Befehlen und Datenzugriffen optimiert.[2]

Auch in Mikrocontrollern, die in eingebetteten Systemen wie Sensoren, Aktoren oder Steuergeräten eingesetzt werden, findet man häufig die Harvard-Architektur, da sie eine geringe Stromaufnahme und eine hohe Zuverlässigkeit ermöglicht. Die Harvard-Architektur erlaubt es, die Mikrocontroller an die spezifischen Anforderungen der eingebetteten Systeme anzupassen, indem sie die Wortbreite und den Speicherbedarf der Befehle und Daten variieren kann.[3] Schließlich wird die Harvard-Architektur auch in spezialisierten Rechnern für künstliche Intelligenz angewendet, die komplexe Algorithmen wie neuronale Netze oder maschinelles Lernen ausführen müssen. Die Harvard-Architektur bietet eine hohe Rechenleistung und eine hohe Parallelisierungsmöglichkeit, indem sie die Befehls- und Datenspeicher getrennt verwaltet.[4]

Einzelnachweise

- ↑ John L. Hennessy, David A. Patterson, Krste Asanović: Computer architecture: a quantitative approach. 5. ed Auflage. Elsevier, Morgan Kaufmann, Amsterdam Heidelberg 2012, ISBN 978-0-12-383872-8.

- ↑ John G. Proakis, Dimitris G. Manolakis: Digital signal processing: principles, algorithms, and applications. 3. ed Auflage. Prentice Hall, Upper Saddle River 1996, ISBN 978-0-13-373762-2.

- ↑ Tammy Noergaard: Embedded systems architecture: a comprehensive guide for engineers and programmers. 2. ed Auflage. Elsevier/Newnes, Amsterdam/Heidelberg 2013, ISBN 978-0-12-382196-6.

- ↑ John L. Hennessy, David A. Patterson, Krste Asanović: Computer architecture: a quantitative approach. 5. ed Auflage. Elsevier, Morgan Kaufmann, Amsterdam Heidelberg 2012, ISBN 978-0-12-383872-8.

Auf dieser Seite verwendete Medien

Autor/Urheber: Sn KGS, Lizenz: CC BY-SA 4.0

Die Harvard-Architektur. Dieses Bild ist eine vektorisierte Version von w:de:Datei:Harvard-architektur.png von w:de:User:Mkleine.